Приступая к изучению языков проектирования цифровых автоматов (vhdl, verilog) хорошо бы знать основы булевой алгебры (алгебры логики) и понимать принципы создания цифровых схем (на логических элементах).

К сожалению эти знания на полу не найдёшь, а объяснять слишком долго и нудно.. Поэтому попытаемся обойтись без большого углубления в них.

Предлагаю смоделировать работу простейшей цифровой схемы в среде разработки ПЛИС Active-HDL.

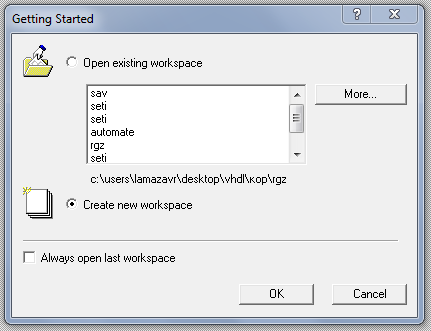

Создаём новый проект.

При запуске студии жмём «Создать новое рабочее место»:

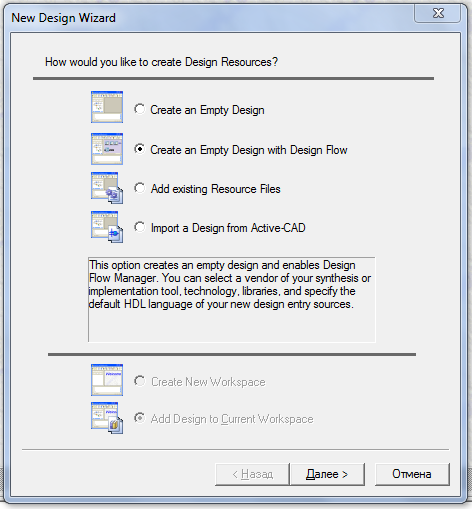

Создаём пустой проект с design flow

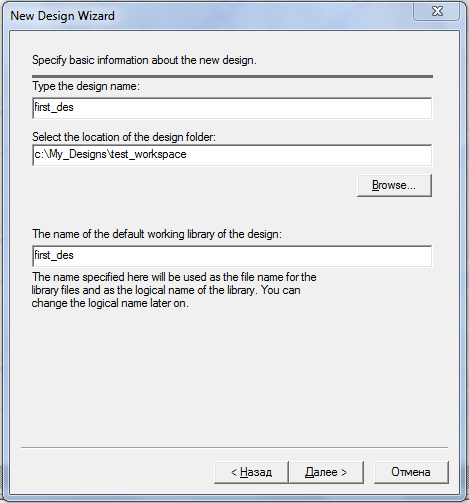

Дальше называем наш design

Дальше действуем по принципу установки программ в Windows..

После окончания создания проекты вы увидите ваше рабочее место:

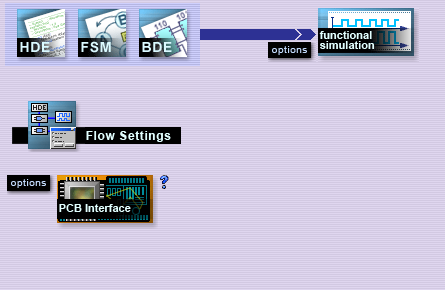

Выбираем редактор схем «BDE» следуя настройкам создаём настройки нашей схемы.

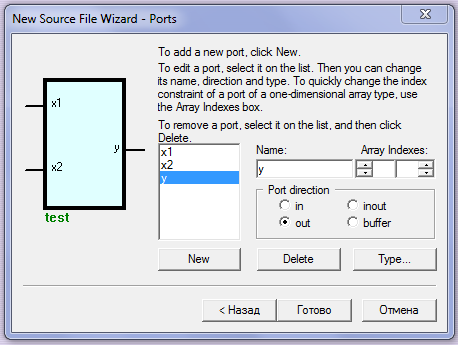

В процессе создания вас попросят указать имя и входы\выходы схемы:

Переключится между входами можно при помощи переключателя Port durection. Выставте входы (in) x1 & x2 и выход y (out).

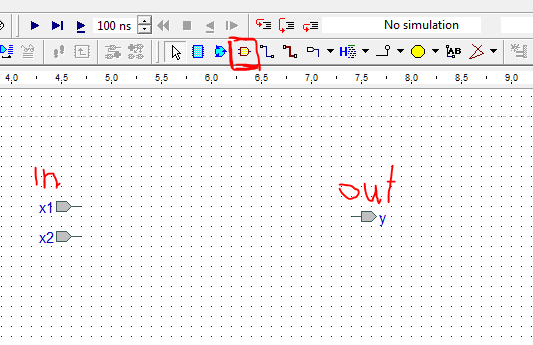

Теперь жмём готово и видем плоды нашего труда:

Слева расположены указанные нами входы, справа — выходы.

Жмум S или кнопку, которую я тщательно обрисовал)))

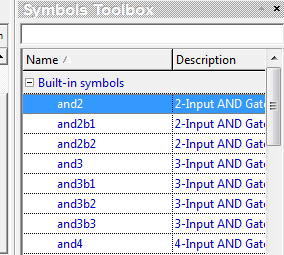

И наблюдаем справа меню элементов:

Тут можем выбрать любой понравившейся элемент и перетащить его на поле схемы. Я выберу and2 (это двухвходовый И)

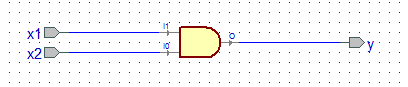

И нарисую вот такую схему:

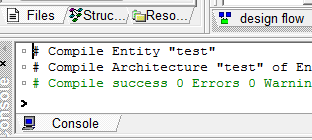

Теперь можно откомпилировать (а вы что думали? это вам не MultiSim) при помощи клавиши F11

Если всё прошло успешно видим сообщение в консоли внизу:

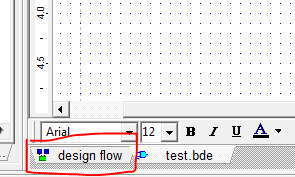

Переключаемся назад на design flow:

Теперь идём в опции симулятора (1), а после настроек (см ниже) жмём на симулятор (2):

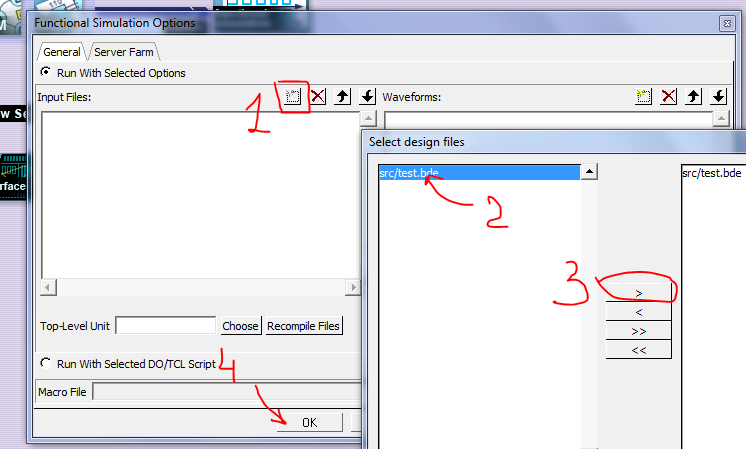

Настройки симулятора:

Добавляем наш файл схемы (1). Выбираем его из списка всех файлов (2) и кликаем по клавише (3) после чего жмём ОК.

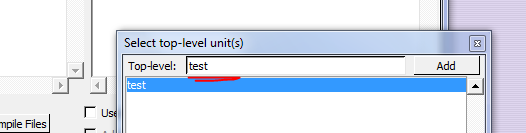

Теперь жмём Choose (она там одна не промахнётесь) и делаем так:

Ну и наконеч жмём ОК (4).

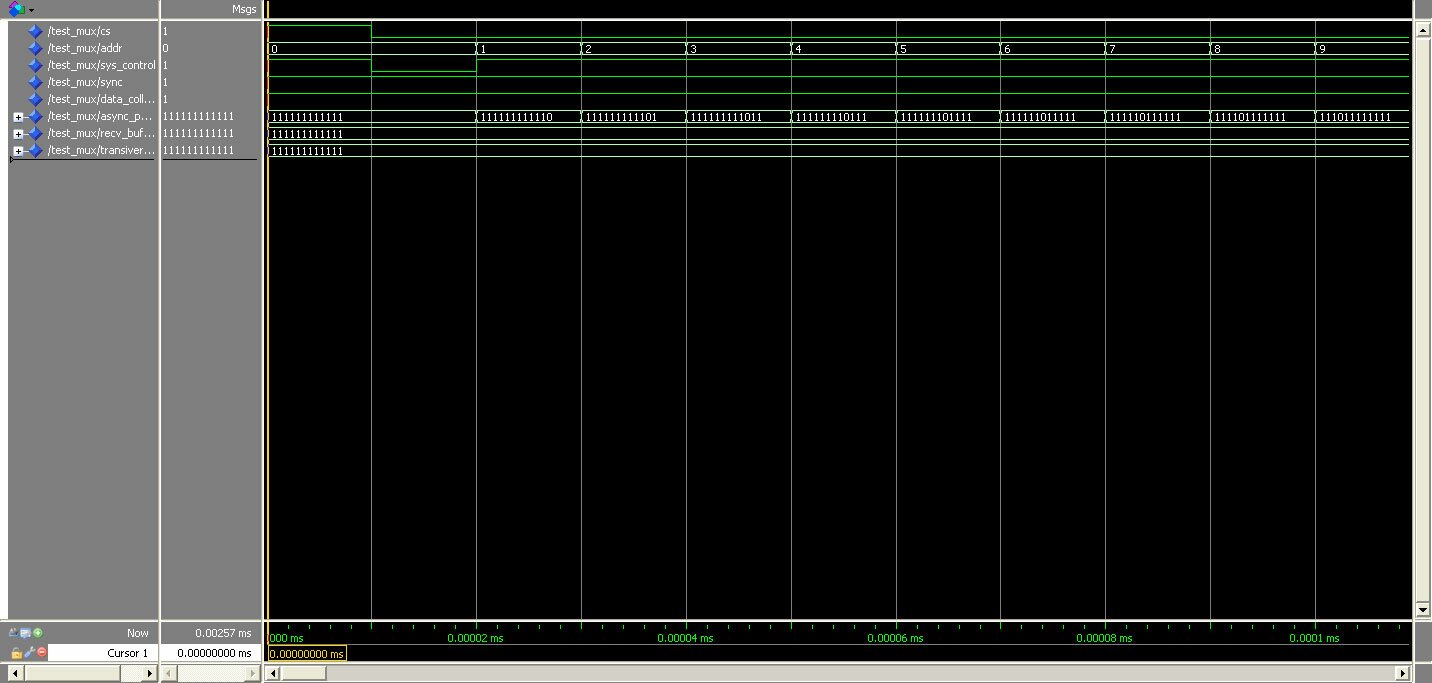

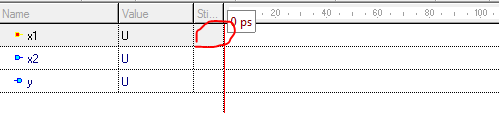

Настройка окончена. После клика по симулятору увидем такое окно:

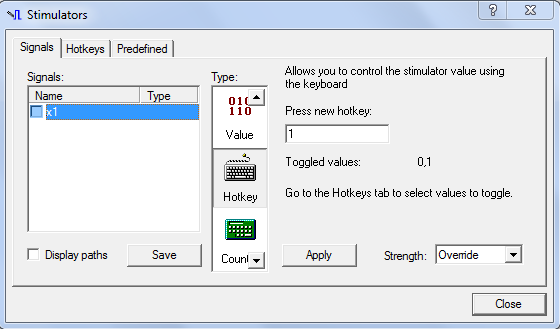

Кликаем в обрисованное поле дважды и указываем там гарячую клавишу для переключения уровня на входе x1:

Не забываем нажать Apply.

Аналогично поступаем с x2 только клавиша пусть будет 2.

Теперь всё готово. Можно моделировать. Надеюсь таблицу истинности элемента И вы знаете.

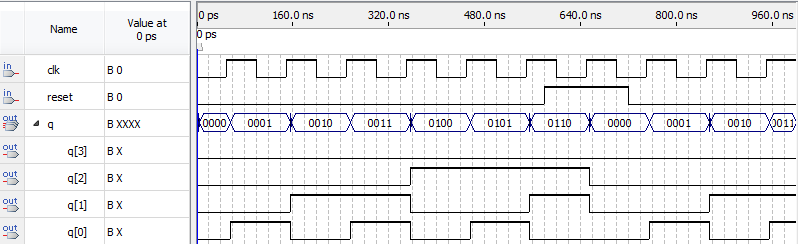

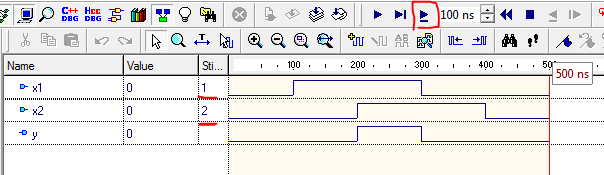

Кликаем клавишу Run For (F5). При этом меняем при помощи клавиш 1 и 2 уровни сигнала.

Видим, что таблица истинности совпала. На выходе y еденица только в случае наличия едениц на обоих входах, в противном случае на выходе 0.

Теперь вы поняли основы работы в среде. Вы можете собирать схемы большей сложности и моделировать их работу не погружаясь даже в основы языка vhdl.

Вы можете создать схему, откомпилировать её, а затем использовать эту схему как элемент (она появится в списке в библиотеках справа). Можно сложные схемы разбирвать на составные части 😉

Дальше будем работать с кодом…